# 10 Gb/s Radiation-Hard Parallel Optical Engine

# K.K. Gan<sup>1</sup>, H.P. Kagan, R.D. Kass, J. Moore, D.S. Smith

Department of Physics, The Ohio State University Columbus, OH 43210, USA E-mail: gan@mps.ohio-state.edu

# P. Buchholz, S. Heidbrink, M. Vogt, and M. Ziolkowski

Fachbereich Physik, Universität Siegen D-57068 Siegen, Germany

We have designed and fabricated a compact array-based optical engine for transmitting data at 10 Gb/s. The device consists of a 4-channel ASIC driving a VCSEL (Vertical Cavity Surface Emitting Laser) array in an optical package. The ASIC is designed using only core transistors in a 65 nm CMOS process to enhance the radiation-hardness. The ASIC contains an 8-bit DAC to control the bias and modulation currents of the individual channels in the VCSEL array. The DAC settings are stored in SEU (single event upset) tolerant registers. Several devices were irradiated with 24 GeV/c protons and the performance of the devices is satisfactory after the irradiation.

38th International Conference on High Energy Physics 3-10 August 2016 Chicago, USA

<sup>1</sup>Speaker

# 1. Introduction

A parallel optical engine is a compact device for high-speed data transmission. The compact design is enabled by readily available commercial high-speed VCSEL arrays. These modern VCSELs are humidity tolerant and hence no hermitic packaging is needed [1]. With the use of a 12-channel array operating at 10 Gb/s per channel, a parallel optical engine can deliver an aggregate bandwidth of 120 Gb/s. With a standard spacing of 250 µm between two adjacent VCSELs, the width of a 12-channel array is only slightly over 3 mm. This allows the fabrication of a rather compact parallel optical engine for installation in locations where space is at a premium. The use of a fiber ribbon also reduces the number of fibers to handle and moreover a fiber ribbon is less fragile than a single-channel fiber. These advantages greatly simplify the production, testing, and installation of optical links.

VCSEL arrays are widely used in off-detector data transmission in high-energy physics [2]. The first implementation [3] of VCSEL arrays for on-detector application is in the optical links of the ATLAS pixel detector. The experience from the operation of this first generation of array-based links has been quite positive. In particular, the failure rate of the optical links fabricated by The Ohio State University is ~0.1% [4]. The ATLAS experiment therefore continued to use VCSEL arrays in the second-generation optical links [5] for a new layer of the pixel detector, the insertable barrel layer (IBL), installed in early 2014 during the long shutdown (LS1) to prepare the Large Hadron Collider (LHC) for collisions at the center-of-mass energy of 13 TeV. In addition, ATLAS also decided to move the optical links of the original pixel detector to a more accessible location. The replacement optical links are also array based.

The optical modules (optical engines or opto-boards) for the two generations of optical links for the ATLAS pixel detector are similar in design. However, there are several improvements in the second-generation opto-boards [5] to increase the reliability of the opto-board and simplify the fabrication procedure. In particular, the optical package (opto-pack) for housing a VCSEL array has a much more robust design [6]. About 400 opto-boards were fabricated, corresponding to about 6,000 uplinks (from the pixel detector up to the counting room) and 3,000 downlinks (from the counting room down to the pixel detector). The links are operated at 40-160 Mb/s.

Based on this extensive and positive experience, it is logical for the ATLAS pixel detector of the high-luminosity LHC (HL-LHC) to continue to deploy optical links using the opto-board concept. In these proceedings, we report the result of an R&D project on the next generation optical engine operating at high speed.

#### 2. Design of the Opto-Board

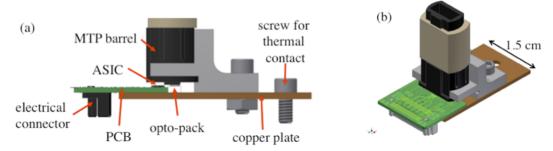

The opto-board is a miniature printed circuit board (PCB). Figure 1 shows a drawing of the opto-board. A VCSEL array driver ASIC is mounted on the opto-board next to an opto-pack. This keeps the length of the wire bonds between the ASIC and the VCSEL array to a minimum to diminish the parasitic capacitance and inductance of the wire bonds. This allows the ASIC to drive the VCSELs at high speed. The PCB has a thick copper back plane (1.0 mm) that can be fastened with a screw to a heat sink to remove the heat generated by the ASIC and VCSEL array. The heat sink can be a copper rail with tube in the center for the passage of coolant. An

MTP barrel attached to an aluminum brace is secured to the opto-board via a screw. A fiber ribbon terminated with a MTP connector can be inserted into the MTP barrel to receive the optical signal from the VCSEL array. The spring-loaded MTP connector is widely used in the optical communication industry due to its ease of use. An electrical connector [7] is attached to the PCB to transmit high-speed data from a pixel module to the VCSEL array driver ASIC. The high-speed electrical signals from the connector to the ASIC are transmitted using controlled impedance differential pair transmission lines on the PCB.

Figure 1: (a) Schematic drawing of an opto-board together with a MTP barrel fastened to the opto-board for the insertion of a fiber ribbon terminated with MTP connector to receive the optical signal from the VCSEL array. (b) A three-dimensional rendition of the setup.

# 3. Design of the Opto-Pack

We have designed an opto-pack that is similar to that used in the second-generation opto-boards for two reasons [6]. First the opto-pack has a simple design and is easy to handle. Second we have extensive experience in fabricating the opto-packs, 1,200 pieces for the second-generation opto-boards. In addition, we have also fabricated 280 opto-packs for the off-detector opto-receivers (RXs). In total, our production volume is equivalent to 18,000 channels, more than what is anticipated for the pixel detector at HL-LHC.

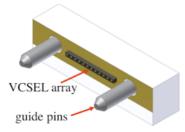

The opto-pack consists of a small BeO block mounted with one optical array and two guide pins as shown in Fig. 2. The design is similar to the opto-pack used in the second-generation opto-boards but with a simplification. The traces for connecting to the common cathode of a VCSEL array are replaced by a plane of solid metal. The BeO substrate is also shorter to minimize the length of the wire bonds between the VCSEL array and the driver ASIC, critical for high-speed data transmission. The two guide pins have their relative position defined by a MT ferrule and fixed with epoxy. The VCSEL array is aligned with respect to the two guide pins to a precision of a few microns. Details of the assembly procedure are given in Ref. [6].

Figure 2: Schematic drawing of an opto-pack. The distance between the two guide pins is 4.6 mm.

#### 4. VCSEL Array Driver ASIC

The VCSEL array driver ASIC was developed under the US Collider Detector R&D (CDRD) program of DOE. This was an R&D program to design a 12-channel VCSEL array driver ASIC for operation at 10 Gb/s. We have prototyped the ASIC in two runs, both in 4-channel versions, using the 65 nm CMOS process of TSMC [8]. The first test chip was submitted for fabrication in October 2014 and the second in March 2016. The dimension of both ASICs is 2 mm x 2 mm. We only use the core transistors of the process in order to achieve maximum radiation tolerance. Both ASICs include an 8-bit DAC to set the VCSEL modulation and bias currents. The DAC settings are stored in SEU (single event upset) tolerant registers. Several improvements were implemented in the second prototype ASIC:

- Eliminated all external biases. All biases are now programmable via DACs. The bias

that is distributed across the ASIC is set via a current and then is converted into a

voltage at the point of use. This allows faster recovery from the signal switching as

there is no large RC constant between the generator of the bias voltage and the point of

use as in the previous scheme.

- Added more on-chip decoupling capacitance of ~200 pF for the whole ASIC.

- Eliminated output feedback amplifier to set output level. One of the modes in the circuit of the first prototype ASIC had large impedance and was virtually an open circuit, causing large jitter, instead of driving the bias voltage.

- Added pre-emphasis to the signal at the receiver output. The location of the added preemphasis is programmable via a delay line.

- Added pre-emphasis and feed through capacitors on the driver block of the ASIC to increase the speed, thereby improving the timing and amplitude control.

- All power lines are tied together and have better power plane. In the first prototype ASIC, each channel has two power pads. In the new ASIC, there are a total of 13 power pads, including some large pads for multiple wire bonds.

#### 5. Results from the First Prototype ASIC

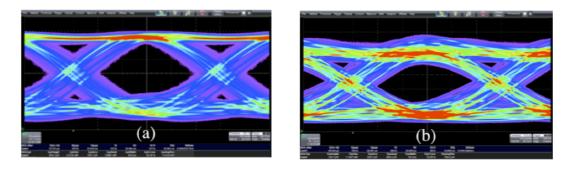

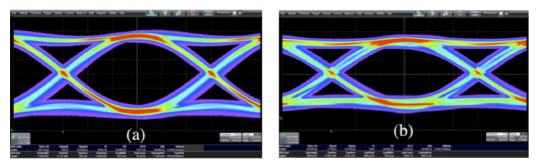

In the first prototype ASIC, all four channels are operational and the bit error rate is less than  $1.3 \times 10^{-15}$  with all channels active using pseudo random bit strings (PRBS) as input. Figure 3(a) shows the optical eye diagram at 10 Gb/s. The eye is open but improvements are needed to reduce the jitter.

The expected radiation level for the optical links depends on the location. For example, if the opto-boards are installed near the outer radius of the endcaps of the silicon tracker ("ID endplates"), the ionizing dose is 10.2 Mrads and the non-ionizing dose is  $5.2 \times 10^{14}$  1-MeV  $n_{eq}$ /cm². In October 2015, we irradiated eight opto-boards with prototype ASICs using 24 GeV/c protons at the CERN PS irradiation facility. In four opto-boards, each ASIC drove a resistive load while in the other four opto-boards, each ASIC drove a VCSEL array [9]. The purely electrical testing would allow us to disentangle the radiation damage of the optical components from that of the ASICs should the opto-boards containing the VCSEL arrays became inoperable after the irradiation. The opto-boards with VCSEL arrays attached were exposed to a dose of  $4.58 \times 10^{14}$  protons/cm², corresponding to an ionizing dose of 12.2 Mrads and a non-ionizing dose of  $2.69 \times 10^{14}$  1-MeV  $n_{eq}$ /cm², assuming that the radiation damage in the VCSEL scales

with the non-ionizing energy loss (NIEL) in the GaAs [10-11]. The opto-boards containing no VCSELs were exposed to a dose of 2.78 x 10<sup>15</sup> protons/cm<sup>2</sup>, corresponding to an ionizing dose of 74.0 Mrads.

Figure 3: Optical eye diagram of a VCSEL channel in the first prototype ASIC operating at 10 Gb/s before (a) and after (b) irradiation.

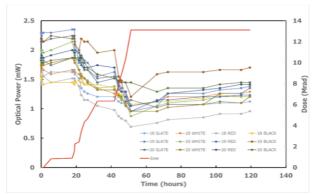

All ASICs were powered and monitored during the irradiation but at reduced speeds because it was not practical to install high-speed cables at the irradiation facility. The optoboards with VCSEL arrays were periodically removed from the proton beam to allow the annealing of the VCSELs that occurred naturally when powered. The optical power as a function of time is shown in Fig. 4. Only 12 out of the 16 VCSEL channels were monitored due to limited number of fiber connections. The optical power decreased during the irradiation as expected and increased (slowly) during the annealing. It is evident that VCSELs still produced good optical power at the end of the irradiation. We will further anneal the arrays to see how much optical power can be recovered.

Figure 4: Optical power of the 12 VCSELs in four arrays as a function of time during irradiation. The red line indicates the dose as a function of time.

All channels were operational at the end of the irradiation and after the radiation cool down, the opto-boards were returned to our lab for characterization of the high-speed performance. The optical eye diagram of one channel after irradiation is compared to that before irradiation in Fig. 3 for 10 Gb/s operation. The optical amplitude decreases from 2.07 to 1.19 mW, consistent with the power loss observed during irradiation. The opening of optical eye diagram is smaller but the device still operates error free for more than 30 minutes, corresponding to a bit error rate, BER  $< 5x10^{-14}$ , with all channels active. Figure 5 shows a

comparison of the corresponding optical eye diagrams for 5 Gb/s operation, the expected data transmission speed of the ATLAS pixel detector at HL-LHC. The eyes are open both before and after irradiation. This is the first demonstration of the radiation hardness of an array driver/VCSEL combination operating at 10 Gb/s with a dose of greater than 10 Mrads.

Figure 5: Optical eye diagram of a VCSEL channel in the first prototype ASIC operating at 5 Gb/s before (a) and after (b) irradiation.

# 6. Results from the Second Prototype ASIC

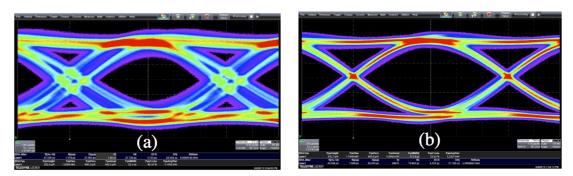

The second prototype ASIC is much easier to tune for operation at 10 Gb/s because of the various improvements listed in Sec. 4. The supply voltage of the ASIC is 1.2 V and the current consumption is 150 mA with all four channels operating at 10 Gb/s. The common cathode voltage is set at -1.3 V in order to provide enough headroom to drive the VCSEL. The current consumption of the common cathode voltage is 25 mA. All channels have excellent coupled optical power, higher than 2 mW. The optical eye diagram is shown in Fig. 6(a) for 10 Gb/s operation. In comparison with Fig. 3(a), the eye is more open but there is significant jitter and this is being investigated. The BER is  $< 5 \times 10^{-14}$  on all channels with every channel active. It should be noted that the wire bonds that connected the driver ASIC to the VCSEL array are somewhat long because the new opto-pack is not yet available. We expect some improvements in the eye diagram with shorter wire bonds. Figure 6(b) shows the optical eye diagram operating at 5 Gb/s, the target data transmission speed of the ATLAS pixel detector at HL-LHC. The eye is wide open, indicating satisfactory performance.

Figure 6: Optical eye diagram of a VCSEL channel in the second prototype ASIC operating at (a) 10 and (b) 5 Gb/s.

#### 7. Conclusions

We have designed and fabricated a new opto-board including an array driver ASIC and optical packaging to allow 10 Gb/s optical data transmission. We demonstrate the radiation

hardness of the combination of a VCSEL array and an array driver ASIC with successful 10 Gb/s operation after irradiation (> 10 Mrads). An improved VCSEL array driver ASIC has been fabricated. The plan is to further improve the design of the ASIC and layout the ASIC in a 12-channel version for application in the ATLAS pixel detector at HL-LHC.

# Acknowledgments

The authors are indebted to Maurice Glaser and Federico Ravotti for their help in using the irradiation facility at CERN. This work was supported in part by the U.S. Department of Energy under contract Nos. DE-SC0011726 and DE-FG-02-91ER-40690, by the National Science Foundation under Grant Number 1338024, and by the German Federal Minister for Research and Technology (BMBF) under contract No. 056Si74.

#### References

- [1] See for example, <a href="http://www.photonics.philips.com/">http://www.photonics.philips.com/</a>

- [2] See for example, G. Aad et al., *The ATLAS experiment at the CERN Large Hadron Collider*, JINST **3** (2008) S08003.

- [3] K. Arms et al., ATLAS pixel opto-electronics, Nucl. Instrum. Methods A. 554 (2005) 458.

- [4] Most of the failures were due to soldering on the optical package used. A more robust package is used in the new ATLAS Pixel opto-boards.

- [5] K.K. Gan et al., Design, production, and reliability of the new ATLAS pixel opto-boards, 2015 JINST 10 C02018.

- [6] K.K. Gan, An MT-style optical package for VCSEL and PIN arrays, Nucl. Instrum. Methods A 607 (2009) 527.

- [7] LSHM connector, Samtec Inc.

- [8] Taiwan Semiconductor Manufacturing Company, Limited.

- [9] The VCSEL array used is V850-2174-002, fabricated by Finisar Corporation.

- [10] A. Van Ginneken, Nonionzing energy deposition in silicon for radiation damage studies, FERMILAB-FN-0522, Oct. 1989.

- [11] A. Chilingarov, J.S. Meyer, T. Sloan, Radiation damage due to NIEL in GaAs particle detectors, Nucl. Instrum. Meth. A **395** (1997) 35.