# **ATLAS Level-0 Endcap Muon Trigger for HL-LHC**

## Haruka Asada\*, on behalf of the ATLAS Collaboration

Nagoya University, Japan

E-mail: asada@hepl.phys.nagoya-u.ac.jp

The design of the Level-0 endcap muon trigger for the ATLAS experiment at the High-Luminosity LHC (HL-LHC) and the status of the system development are presented. The HL-LHC is planned to start the operation in 2026. The peak luminosity will ultimately reach  $\mathcal{L} = 7.5 \times 10^{34} \, \text{cm}^{-2} \text{s}^{-1}$ . The new Level-0 endcap muon trigger system reconstructs primitive muon candidates using Thin Gap Chamber (TGC) hits with an improved momentum resolution to suppress the trigger rate, while achieving an efficiency better than the current system. A high-speed serial link between TGC on-detector and off-detector boards with the recovery clock was demonstrated, and the bit error ratio was found to be lower than  $4.8 \times 10^{-16}$ . The track reconstruction of primitive muon candidates is based on a pattern-matching algorithm using predefined sets of hits corresponding to tracks. An initial test of the algorithm with the Xilinx evaluation kit VCU118 showed a high efficiency with reasonable memory resources. The muon candidate selection with several subdetectors in the inner layers was demonstrated, using Monte Carlo simulation samples produced with HL-LHC conditions. The selection efficiency for a single muon was estimated to be greater than 90%, a few percent higher than the current system. The rate was evaluated with protonproton collision data taken with the random trigger overlaid to account for a number of pileup events of 200, which is expected at the HL-LHC. The obtained value for the momentum threshold of 20 GeV, the primary threshold assumed for a single muon trigger, is about 30 kHz. Precise momentum determination by Monitored Drift Tube is expected to further reduce the rate.

European Physical Society Conference on High Energy Physics - EPS-HEP2019 - 10-17 July, 2019 Ghent, Belgium

<sup>\*</sup>Speaker.

# 1. Introduction

The upgrade of the ATLAS Level-0 endcap muon trigger is required to satisfy the physics requirements of the ATLAS experiment [1] at the High-Luminosity LHC (HL-LHC) [2]. The HL-LHC is planned to start in 2026 for precision measurements of the standard model and searches for new physics with higher luminosity. The ATLAS experiment will ultimately accumulate a data set of about  $4000 \text{ fb}^{-1}$  with ten years of operation. At the HL-LHC, the instantaneous luminosity will reach  $7.5 \times 10^{34} \text{ cm}^{-2} \text{s}^{-1}$ . The Level-0 trigger rate at ATLAS will be up to 1 MHz. The endcap muon trigger system needs to be upgraded to cope with higher instantaneous luminosity [3]. In this report, an overview of the new trigger and status of the system development are described.

#### 2. ATLAS Level-0 endcap muon trigger for the HL-LHC

## 2.1 Overview of the new Level-0 endcap muon trigger

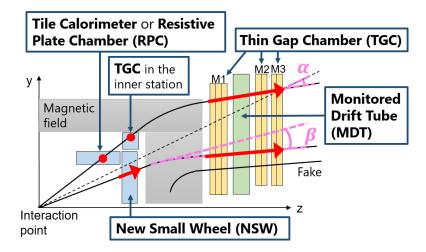

A schematic view of muon detectors which provide input signals to the Level-0 endcap muon trigger [3, 4] is shown in Figure 1. The Thin Gap Chamber (TGC) [5] is used for fast segment reconstruction in the outer region of the magnetic field. The Tile Calorimeter [6], Resistive Plate Chamber (RPC) [5], TGC in the inner station [5], and New Small Wheel (NSW) [7] provide position and angular information in the inner region. The Monitored Drift Tube (MDT) [5], which is newly introduced for the HL-LHC hardware trigger, is used for precise segment reconstruction in the regions of interest provided by the TGC.

**Figure 1:** The overview of the Level-0 endcap muon trigger algorithm with the muon detectors [3]. TGC consists of seven layers. The layers are grouped as stations called M1, M2, and M3, respectively. Two black curves from the interaction point show muon tracks. The other black curve shows fake tracks. The red arrows indicate the track segments reconstructed by the TGC, MDT, and NSW. The red points indicate the hit positions of muons detected by the Tile Calorimeter, RPC and TGC in the inner station.

The Level-0 endcap muon trigger is designed to be sensitive to muons whose transverse momentum  $(p_T)$  is greater than 4 GeV. The track parameters,  $\alpha$  and  $\beta$ , used to deduce the transverse momentum of the trigger candidates can be seen in Figure 1. In the pseudorapidity  $\eta$  range of

$1.05 \le \mid \eta \mid \le 1.3$ , the muon  $p_T$  is determined from the angle  $\alpha$ . This is defined as the polar angle of the TGC track segment with respect to the vector from the interaction point to the segment position, and the position matching between the TGC track segment and the hits in the Tile Calorimeter, RPC, and TGC in the inner station. In the range of  $1.3 \le \mid \eta \mid \le 2.4$ , muon  $p_T$  is determined from the angle  $\beta$ , defined as the polar angle difference between the NSW track segment and the TGC track segment.

The hit data in the inner detectors are essential to reject fake muon tracks, which are not originating from the interaction point. MDT track segment is employed to refine the muon candidate seeded by the other detectors.

#### 2.2 Hardware design of the trigger system

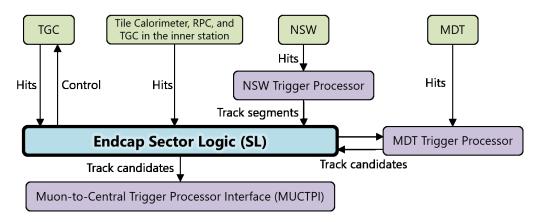

The main components of the trigger system are the NSW Trigger Processor, MDT Trigger Processor, and Endcap Sector Logic (SL). The block diagram of the system is shown in Figure 2. First, the Endcap SL reconstructs TGC track segments using TGC hits. Then, the Endcap SL takes a coincidence with the Tile Calorimeter, RPC, and TGC in the inner station, and evaluates  $\alpha$ . The Endcap SL also evaluates  $\beta$  from TGC and NSW track segments. After that, the Endcap SL sends the candidates to the MDT Trigger Processor. The MDT Trigger Processor overwrites the  $p_T$  of the candidates with better momentum resolution of MDT hits, which have better position resolution. The candidates are sent back to the Endcap SL. Finally, the Endcap SL sends the candidates to the Muon-to-Central Trigger Processor Interface (MUCTPI).

Figure 2: Simplified block diagram of the Level-0 endcap muon trigger system for the HL-LHC [3].

The Endcap SL system consists of 48 ATCA blades. To realize the new trigger system, each Endcap SL is required to have about a hundred pairs of optical receivers and transmitters to receive detector signals and control on-detector electronics. The Endcap SL should have a few hundred Mbits of memory resources to reconstruct TGC track segments. The Xilinx Virtex Ultra-Scale+ FPGA, XCVU9P [8], is proposed to be implemented on the Endcap SL module to operate transceivers and the trigger algorithm.

# 3. Demonstration of the trigger system on hardware

# 3.1 Clock handling scheme for the TGC electronics

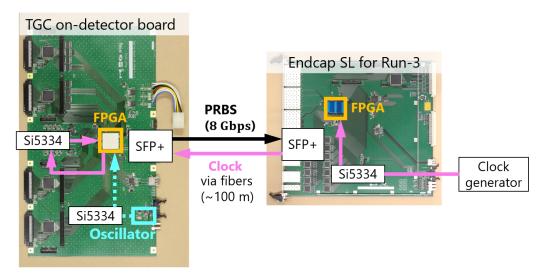

The Endcap SL communicates with the TGC on-detector boards using optical links with a bandwidth of 8 Gbps per link. The TGC on-detector boards transfer the hit data to the Endcap SL, and the Endcap SL transfers control signals to the TGC on-detector boards. The TGC on-detector boards are synchronized with the Endcap SL using the recovery clock generated at the receiver of the optical link.

A demonstration was performed to validate the operation scheme with the recovery clock. The TGC on-detector board prototype for the HL-LHC and the Endcap SL prototype for Run 3 were employed. Figure 3 shows the setup of the demonstration. The on-detector board sends a 31-bit pseudo-random binary sequence instead of TGC hit data. No bit error was detected for the duration of the demonstration, which was approximately three days. The upper limit of the bit error ratio is  $4.8 \times 10^{-16}$ .

**Figure 3:** The setup of the demonstration of clock transfer. Each board has a Kintex-7 FPGA [8]. The solid arrows show the paths of the data and the clock, which are synchronized to the clock generator output. The dashed arrow shows the path of the clock used to receive the data from the Endcap SL.

#### 3.2 TGC track segment reconstruction

The reconstruction of TGC track segments with pattern-matching is under study. The algorithm has two steps. The first step is to take a coincidence of TGC hits within each station, M1, M2, and M3. The next step is segment extraction using the outputs of the station coincidence. The segment position, angle  $\alpha$ , and  $p_T$  threshold are extracted from look-up tables, which are implemented in UltraRAMs of Virtex UltraScale+ FPGA.

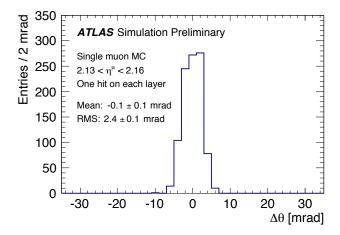

An initial test of the TGC track segment reconstruction was performed. A test firmware for a pseudorapidity range of 2.13–2.16 was developed on XCVU9P FPGA of the evaluation kit VCU118 [10]. The TGC hits of 1000 single muons with  $p_T = 20$  GeV generated using Monte Carlo simulation are used as the input data. Each event is required to have exactly one hit on each

layer. The output data are the TGC track segments. The segments were reconstructed successfully for all events. Figure 4 shows the distribution of the polar angle difference ( $\Delta\theta$ ) between the truth information and the outputs of the trigger algorithm. In this test, UltraRAM usage for the channel list is about 0.52 Mbit. The expected memory size for the whole channel list is about 100 Mbit. It is about one-third of the RAM resources on XCVU9P. The obtained RMS value of the distribution in Figure 4 is consistent with the angular resolution estimated from the width of TGC channels.

**Figure 4:** Distribution of the polar angle difference ( $\Delta\theta$ ) between truth segments and TGC segments reconstructed by a pattern-matching algorithm working on an XCVU9P FPGA [11].

# 4. Evaluation of trigger performance

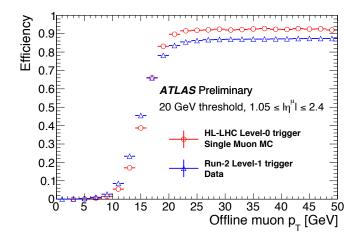

The efficiency of the Level-0 endcap muon trigger was evaluated for the whole region of the system, in the pseudorapidity range  $1.05 \le |\eta| \le 2.4$ . The trigger algorithm assumed for the Endcap SL described in Section 2 was emulated by software. A Monte Carlo sample for one muon track per event is used. Figure 5 shows the trigger efficiency for a  $p_T$  threshold of 20 GeV, where the efficiency for the Run 2 system is shown as a reference. The efficiency of the new algorithm is higher by a few percent in the plateau region. It results from different coincidence schema, described in the following. In the Run 2 system, more than one hit in three layers of the station M1 and more than two hits in four layers of the station M2 and M3 are required in the early stages of the algorithm. In the new algorithm, a relaxed coincidence of more than four hits in seven layers of the stations M1, M2 and M3 is implemented by exploiting all TGC hits available in the Endcap SL. An improvement in  $p_T$  resolution by the TGC segment reconstruction algorithm leads to a better rejection of low- $p_T$  muons.

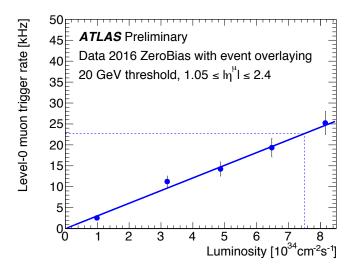

The Level-0 single muon trigger rate in the endcap region was estimated for a 20 GeV  $p_{\rm T}$  threshold, with Run 2 data taken with a random trigger overlaid to account for higher luminosity. The result is shown in Figure 6. The rate has a first-order correlation with the luminosity. It indicates that accidental coincidence is under control. The rate in the endcap region is less than 30 kHz for the expected luminosity at the HL-LHC. Further rate reduction in the precision step of MDT is expected.

**Figure 5:** Expected efficiency for the Level-0 endcap muon trigger with the new algorithm (circles) and that for the Level-1 endcap muon trigger with the Run 2 system (triangles) [11].

**Figure 6:** The expected rate for the Level-0 endcap muon trigger with the HL-LHC scheme [11]. The solid line indicates the results of a linear fit, crossing the origin. The dashed lines show the expected rate at the ultimate luminosity  $(7.5 \times 10^{34} \text{ cm}^{-2} \text{s}^{-1})$  of the HL-LHC.

#### 5. Conclusion

The ATLAS endcap muon trigger has to be replaced for the HL-LHC. The new Level-0 system is developed based on fast track segment reconstruction to realize the trigger, which is more flexible and has better performance than the current one. The data transfer between the Endcap SL and the TGC on-detector board with the recovery clock was demonstrated. The upper limit of the bit error ratio was  $4.8 \times 10^{-16}$ . An initial test of TGC track segment reconstruction with a pattern-matching algorithm on an XCVU9P FPGA was performed. All TGC segments were successfully reconstructed. An estimated memory resource for the channel list is about 100 Mbit. The performance of the Level-0 endcap muon trigger was evaluated. A Monte Carlo sample for one

muon track per event and Run 2 data taken with a random trigger are used to evaluate the trigger efficiency and the trigger rate, respectively. The new algorithm shows a higher efficiency, by a few percent, than the current system. The Level-0 rate for the endcap single muon trigger, for a 20 GeV  $p_{\rm T}$  threshold, is less than 30 kHz. The MDT track trigger is expected to reduce the rate further.

#### References

- [1] ATLAS Collaboration, The ATLAS Experiment at the CERN Large Hadron Collider, JINST 3 (2008) S08003.

- [2] G. Apollinari, I. Béjar Alonso, O. Brüning, P. Fessia, M. Lamont, L. Rossi and L. Tavian, High-Luminosity Large Hadron Collider (HL-LHC): Technical Design Report V. 0.1, CERN-2017-007-M.

- [3] ATLAS Collaboration, Technical Design Report for the Phase-II Upgrade of the ATLAS TDAQ system, CERN-LHCC-2017-020.

- [4] ATLAS Collaboration, Technical Design Report for the Phase-II Upgrade of the ATLAS Muon Spectrometer, CERN-LHCC-2017-017.

- [5] ATLAS Collaboration, ATLAS muon spectrometer: Technical Design Report, CERN-LHCC-97-022.

- [6] ATLAS Collaboration, ATLAS tile calorimeter: Technical Design Report, CERN-LHCC-96-042.

- [7] ATLAS Collaboration, New Small Wheel Technical Design Report, CERN-LHCC-2013-006.

- [8] Xilinx Inc., https://www.xilinx.com/ (accessed on September 4th, 2019).

- [9] Xilinx Inc., UltraScale Architecture Memory Resources User Guide (v1.10), UG573, February 4th, 2019.

- [10] Xilinx Inc., VCU118 Evaluation Board User Guide (v1.4), UG1224, October 17th, 2018.

- [11] ATLAS Collaboration, Level-0 TGC Trigger Performance of trigger algorithms in software and firmware implementations,