# The Upgrade Project for the CMS Pixel Detector

# Wilhelm Bertl<sup>1</sup> for the CMS Collaboration

Paul Scherrer Institut 5232 Villigen PSI, Switzerland E-mail: wilhelm.bertl@psi.ch

A substantial upgrade of the CMS pixel detector is foreseen to replace the existing detector in early 2017. In particular, the upgrade aims to improve CMS tracking and vertexing for the momentum range below 10GeV/c, the most important region for B-tagging, even in the presence of many overlapping pile-up events. The goal will be achieved by adding one sensitive barrel pixel layer and two forward/backward disks while keeping the total mass of the detector below the current amount within the tracking region. This detector enlargement has consequences for the power provision, for the cooling system and the readout electronics. In this paper most of the changes will be addressed and the anticipated tracking improvements will be given.

The 20th Anniversary International Workshop on Vertex Detectors – Vertex 2011 Rust, Lake Neusiedl, Austria (June 19 – 24, 2011)

<sup>1</sup> Speaker

© Copyright owned by the author(s) under the terms of the Creative Commons Attribution-NonCommercial-ShareAlike Licence.

# 1. Introduction

The pixel detector of CMS has an installation scheme that allows replacement even in short yearly technical shutdowns [1]. In case of performance degradation of the innermost layer due to intense hadronic irradiation the installation procedure makes replacements relatively easy. We are planning to replace the current 3 layer pixel hit system with a new 4 hit system in the shutdown 2016/17.

In order to keep the design and construction time of the updated pixel detector within limits, we have modified the existing system to cope with an extended LHC luminosity of up to  $2 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. To make this transparent the upgrade has been called phase-1 in contrast with phase-2, supposed to be the final upgrade to an HL–LHC scenario.

The basic concept of the pixel detector upgrade foresees improvements on tracking quality, impact parameter resolution and rate capability. However, building a new pixel detector is not only constrained by technical feasibility and space limitations but also from the operation schedule of LHC and CMS. The pixel phase-1 upgrade has to proceed during normal LHC and CMS operation with only limited technical shutdown interruptions and therefore does not allow significant changes of the installation procedure or relevant CMS components. This restriction concerns, in particular, the power lines, the cooling pipes and the read-out fibers within the service channels which pass through the whole body of CMS. Those cannot be replaced and only very limited modifications are possible.

#### 2. Improvement of tracking

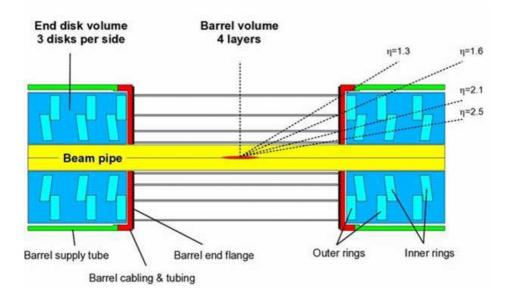

Track elements reconstructed by the pixel detector are used as seeds for full track reconstruction. More precise determination of pixel tracks therefore improves tracking efficiency, reduces fake tracks, improves vertex finding and helps in high level triggering, too. Pixel tracking can be improved by increasing the number of recorded hits per track element. This will be accomplished by adding a fourth layer to the barrel part and a third disk in both forward detector parts (fig.1). With this design each track, up to a pseudorapidity of  $\eta = 2.5$ , will normally have four hits - one more than in the presently installed detector.

However, tracking will benefit from an additional hit only if the total mass of the detector does not increase proportional to the number of detection layers. Simply adding a barrel layer and two disks using the same technology as for the present detector would result in a mass increase by more than 50%, thereby ruining the benefit of the fourth hit. In designing the new detector all components were examined with the goal of lowering their mass. The new concept promises a weight for the 4-layer barrel part of 7950g (within  $\eta = 2.15$ ) as compared with 15840g of the existing 3-layer detector within the same pseudorapidity range. Expressed in radiation length this will be a reduction by at least 20% of the previous value in the barrel region  $\eta \leq 1.3$  and a larger reduction at higher  $\eta$ .

**Figure 1.** Shown is a schematic drawing of the proposed pixel detector indicating the covered pseudorapidity range. Four concentric cylindrical layers make up the barrel part. The forward and backward parts consist of three disks each of them split into two halves.

The mass reduction for the forward/backward parts will be somewhat smaller with only 20% within  $\eta = 2.5$ , but the reduction in terms of radiation length will be even larger - expected are 50% of the present design – due to different material composition. Those expected values have been already partly verified by constructing test structures of crucial detector elements.

The biggest share in mass reduction is accomplished in going from liquid  $C_6F_{14}$  cooling as used in the present detector to a double-phase evaporative  $CO_2$  cooling system. The excellent thermodynamic properties of two-phase  $CO_2$ , like small viscosity, high heat transfer, high latent heat and low liquid/vapor density ratio enables the use of small cooling tubes (typically 1.6/1.8mm inner diameter) which can easily stand the high pressure operation (typically 20bar) mandatory for this cooling technique. Additional advantages are the low mass of carbondioxid, its radiation hardness and last not least its cheapness [2].

Further gains in the material budget are achieved by thinning down the read-out chips at least for the innermost barrel layer, a new mechanical design based on CFK/foam structures, micro twisted pair cables and a new concept for the service tube which shifts most of the unavoidable material from the sensitive tracking region out to areas with  $\eta > 2.2$ .

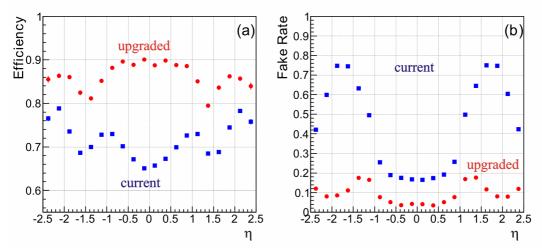

Fig. 2 shows the expected improvement in efficiency and fake rate suppression for the new 4-pixel hit detector. Fake rate suppression is most effective for very low transverse momentum ( $\leq 2$ GeV/c) while efficiency is gained over the full momentum range.

**Figure 2.** Expected improvement of tracking efficiency (a) and fake rate suppression (b) assuming pixel track seeding by the present detector (blue) and the upgraded one (red). The plots cover the full range of pseudorapidity which can be accessed by tracking in CMS.

#### 2.1 Impact parameter resolution

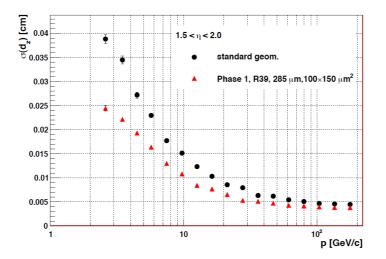

Improved tracking quality using more detection layers with less mass as described above leads already to a significant improvement of impact parameter resolution (see fig. 3). Bringing the innermost detection layer closer to the interaction point could improve it further. Shrinking the innermost layer in radius is technically possible as the beam pipe will be replaced by a new device with a radius of 21.7mm instead of 29.0mm as used now. A detailed mechanical design already exists on how to move the barrel detector as close as possible to the beam pipe without touching it.

There is, however, a potential problem with the high rate at a radius of ~3cm which could lead to unacceptable dead time in the read-out frontend chip. Studies to clarify this point are under way, but until the situation has clarified both layer-1 options are followed further. The two options for barrel layer-1 are: a layer using 16 sensor faces at a radius of 3.9cm or, alternatively, a layer using 12 faces at a radius of 2.9cm.

#### 3. Improvement of readout electronics

The present pixel detector uses the readout chip (ROC) version PSI46V3 with an internal double column drain mechanism and an analog coded data transfer at 40MHz to a Token Bit Manager (TBM, mounted on the front end module) which initiates the data transfer upon a L1-trigger and sends the data via optical links to the Front End Driver (FED) located in the counting room. The ROC as well as the TBM has been designed to work with only 1-2% data losses at a luminosity of  $10^{34}$ cm<sup>-2</sup>s<sup>-1</sup> and a bunch crossing separation of 25ns [3]. For the years right after 2017 the expectations for LHC are that the luminosity likely will increase to  $2 \cdot 10^{34}$ cm<sup>-2</sup>s<sup>-1</sup> eventually with a bunch crossing distance of 50ns. With such an operating scenario the innermost barrel layer will become 50% inefficient, clearly an unacceptable situation.

**Figure 3.** Shown are simulation results of the longitudinal impact parameter resolution for the present forward detector (black) and the upgraded one (red). If the innermost barrel layer is chosen as a 12 face cylinder at a radius of 2.9cm a further 75% reduction of the red curve at low momentum is anticipated.

In addition, there is a problem with the data readout as the increase of detector modules caused by the additional layers cannot be compensated by an adequate increase of the number of optical readout fibers. The analog coded data transfer is with 40MHz already close to its rise-time limit and therefore the transfer frequency cannot be raised for analog data.

In order to accommodate the problems listed above a new ROC is under design, called PSI46dig. Most important changes are the replacement of the analog data transfer by a digital readout and a substantial increase of the number of local data buffers. The frontend amplifier, threshold and trimming mechanism and the column drain technique will not be changed. The new chip will also remain with the 0.25µm IBM technology. Submission is planned for November 2011. In a further submission likely in July 2012 changes to the internal parts of the column drain mechanism are planned in order to reduce the dead time for layer-1 at a radius of 2.9cm to tolerable levels. These changes are invisible for the external operation of the ROC.

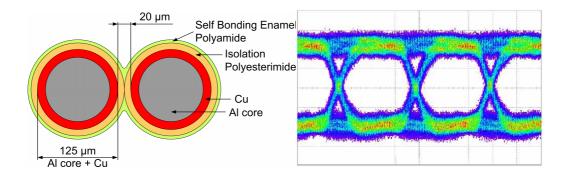

Digitization will be performed by an on-chip 8-bit ADC at a speed of 80MHz. The design of the radiation hard ADC is completed as is the development of a PLL featuring 80MHz. Digitized data are sent with 160MHz from the ROC to the TBM where the frequency is once more doubled to 320MHz. A staged upgrade of the TBM chip has been launched which will deal with the digitized signals at this frequency and, in addition, will have an option included to suppress background due to beam gas interactions. Cables to transfer those signals to the optical transmitter (POH) have been successfully tested (see Fig. 4). On the FED the required changes can be achieved by proper modification of some daughter boards.

The new ROC "PSI46dig" will house an increasing number of data buffers for each pixel double column (80 instead of 32) as well as time stamp buffers (32 instead of 12). 64 on-chip readout buffers each 24-bit long keep the readout losses at acceptable low levels (1-2%) even for maximum trigger rates. In combination with the improvements planned for the double column drain as mentioned above the new ROC is able to operate at a particle rate of almost  $600MHz/cm^2$  and a L1-trigger rate up to 100kHz.

**Figure 4.**Left side: Cross section of a micro twisted pair cable consisting of copper-cladded aluminum wires (CCA) establishing the 1m long link from the TBM on the frontend modules to the optical transmitter (POH). Radiation hard driver chips have been built and tested with cable prototypes. The resulting eye-diagram for 320MHz is shown on the right with 40mV level spacing.

In the redesign procedure of the ROC several other topics have been addressed, understood and solved as there are sources of crosstalk affecting the pixel threshold and deviations from pulse height linearity. The chip power-up behavior will be improved and a couple of DACs found to be unnecessary will be omitted from the new ROC in order to save power.

## 4. Consequences for chip powering

Estimation of the power requirement indicates that the power consumption of the new ROC will be very similar to the existing one. Scaling up the number of modules as needed for 4 barrel layers and having to refrain from changing the power cables would lead to a power loss in the cables of approximately 4kW. Such losses would amount for more than 50% of the total power need and means not only a highly ineffective usage but also an overheating risk for the cables. In addition, the C.A.E.N A4603 power supplies won't be able to support such a request, requiring a complete new design.

This power problem for the barrel pixel detector can be solved using DC-DC-converters close to the detector which would transform voltage into current and therefore reducing the cable losses. A radiation hard DC-DC-converter has been developed and successfully tested under realistic conditions [4]. A relatively small modification of the existing C.A.E.N A4603 power supplies will make them compatible with the DC-DC-converter.

Availability of sufficient power is a less severe problem for the forward/backward pixel detectors. Cables and power supply units have been already foreseen for a third disk in the original planning for the pixel detector. However, in order to keep the power system equal for all pixel detector components, the modified system will be used for the forward/backward detector, too.

## 5. Conclusion

All parts of the CMS pixel detector – the barrel part and the two forward/backward parts – will be replaced in 2017 by refurbished and significantly enhanced devices. The major enhancement comes from more sensitive layers in order to increase the average hit number on pixel tracks from 3 to 4 while simultaneously reducing the total detector mass in the sensitive tracking volume. Apart from many small improvements in mechanics and module production the largest gain in mass savings comes from the replacement of the liquid  $C_6F_{14}$  to an evaporating CO<sub>2</sub> cooling system. Tracking quality and vertex finding will improve significantly in particular in the momentum range below 10GeV/c important for B-tagging.

Side effects of this tracking improvement are necessary changes in the data readout and the power provision because replacing readout fibers and supply cables is virtually impossible in available technical shutdown periods of LHC. The upgrade of the data readout is also driven by the insight that the LHC operation mode beyond 2017 might differ from what was expected for the design of the present pixel detector. In particular, luminosities up to  $2 \cdot 10^{34} \text{ cm}^{-2} \text{s}^{-1}$  and bunch crossing distances longer than 25ns seem to become likely scenarios. With such operating conditions the current readout mechanism would create unacceptable dead time losses of order 50% in the innermost layer. The first submission of the modified ROC and TBM chip will be made in fall 2011.

Mechanical prototypes of barrel and disk elements and of the supply cylinders have been constructed demonstrating the required rigidness while reducing its mass significantly. Effort has started to implement the new design into CMS simulation software.

In 2013 during the anticipated long shutdown of LHC the new  $CO_2$  cooling system and the modified power system will become available for testing detector prototypes and dummies. Production of phase-1 detection modules will then commence in several production centers around the world. Completion of the phase-1 pixel detector is expected in early 2016 followed by extensive commissioning periods before being installed into CMS in an extended technical shutdown 2016/2017.

The author would like to acknowledge the numerous and very helpful discussions with many members of the CMS pixel.

#### References

- [1] A. Cattai et al, CMS Tracker Technical Design Report, CERN/LHCC 98-6, 15.April 1998.

- [2] H. Postema, Cooling in HEP Vertex and Tracking Detectors, in proceedings of this conference.

- [3] CMS Collaboration, The CMS Experiment at the CERN LHC, J. Instrum. 3 (2008) S08004.

- [4] K. Klein, *Powering for Future Detectors*, in proceedings of this conference.