# Microchannel Cooling techniques at LHCb

# Oscar Augusto de Aguiar Francisco\*

on behalf of the LHCb VELO Upgrade and CERN PH-DT groups CERN (CH) E-mail: oscar.augusto.de.aguiar.francisco@cern.ch

The thermal management of the LHCb Vertex Detector Upgrade will be provided by evaporative  $CO_2$  circulating in micro-channels or thin tubes. The main plan is to use micro-channels embedded in silicon due to its excellent cooling performance, no thermal expansion coefficient mismatch with electronics and minimal material budget. However, two back-up alternatives are also being investigated: stainless steel tubes embedded in ceramics and titanium 3D printing. The latest prototyping results concerning all cooling substrates alternatives will be described in this proceedings.

The 26th International Workshop on Vertex Detectors 10-15 September, 2017 Las Caldas, Asturias, Spain

#### \*Speaker.

<sup>©</sup> Copyright owned by the author(s) under the terms of the Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License (CC BY-NC-ND 4.0).

#### 2 1. Introduction

The LHCb Vertex Detector (VELO) will be upgraded in 2018 to a lightweight pixel detector 3 capable of 40 MHz readout to operate at higher luminosity (x5 higher than the current) and very 4 close (5.1 mm) to the LHC beams [1, 2]. Each module is composed of 4 sensors, 12 ASICs and two 5 transceivers (GBTx) that will dissipate around 30 W in the end of the detector lifetime. To minimize 6 the amount of material close to the beam, the electronics (sensor + ASIC) will be overhanging the cooling substrate by 5 mm in innermost region. The sensors should be kept below -20 °C to prevent 8 thermal runaway while the expected temperature of the boiling CO2 will be around -30°C. No leaks 9 can be tolerated since the detector will operate under vacuum. At room temperature, the pressure 10 of the boiling CO<sub>2</sub> is around 65 bar and, according to the CDERN safety regulations, the cooling 11 substrates should be validated up to 186 bar (safety factor of 2.86). Therefore, a new cooling system 12 is necessary due to the new conditions. 13 Though micro-channel cooling embedded in a silicon plate is gaining considerable attention 14 for applications related to microelectronics, it is still a novel technology for particle physics ex-15

periments, in particular when combined with CO<sub>2</sub> evaporative cooling. This technique provides excellent thermal efficiency, no thermal expansion mismatch with silicon ASICs and sensors, radiation hardness of CO<sub>2</sub>, and a very low contribution to the material budget. In parallel to the development of the micro-channel substrate embedded in silicon, the VELO group is also working on the development of two cooling substrate alternatives: capillaries embedded in a ceramic and 3D printed titanium. The latest results concerning all cooling approaches will be described in next sections.

## 23 2. Micro-channel embedded in silicon

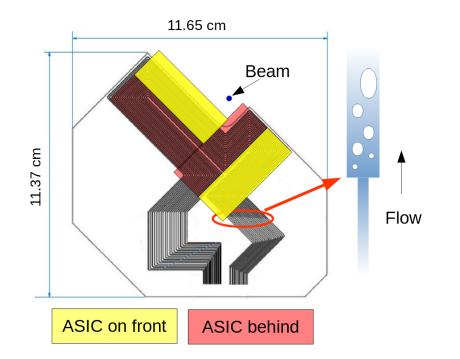

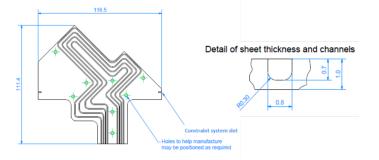

Micro-channels are composed of two parts: restriction and main channels. The restrictions 24 (60 µm by 60 µm and 4 cm long) are located before the entrance to a race-track layout of the main 25 cooling channels. They are the dominant pressure drop and ensure even distribution of coolant and 26 prevent flow instabilities among the channels. The sudden increase in cross section between the 27 restrictions and the main channels (120 µm by 200 µm) triggers the boiling of the CO<sub>2</sub>. All channels 28 have almost the same length in total (around 30 cm). Therefore, all channels have similar fluidic 29 resistance. The power dissipation is mainly produced by the six ASIC on front and six located on 30 the back of the substrate (up to 2 W each). Figure 1 shows the design of the micro-channels. 31

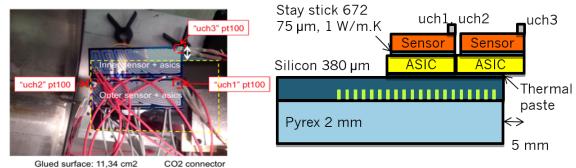

The cooling performance was simulated using the ANSYS sofware [3]. In this simulation, 32 the power dissipation of 3 W per ASIC was considered (36 W in total) and the attachment to the 33 substrate was simulated as a layer of 100  $\mu$ m of stycast 8550 FT + catalyst 9 (1.25 W/(m.K)). The 34 hottest are is in region overhanging by 5 mm. The maximum variation of temperature is around 5 °C 35 when the temperature of the CO<sub>2</sub> is -30 °C. A experimental setup that mimics half of a module was 36 also developed as illustrated in the Figure 6. The power dissipation was generated by special heaters 37 designed to simulate the heat pattern in the ASICs and sensors. In total, a power dissipation of 13 W 38 was generated to simulate the end-of-lifetime expectation. This power dissipation corresponds to 39 the expected heat produced by the ASICs ( $6 \times 2$  W) plus the heat produced by the innermost sensor 40

**Figure 1:** Design of the micro-channels showing the race-track layout and the interface between restrictions and main channels. The heat provided by the electronics is absorbed by the boiling  $CO_2$  in the main channels.

$_{41}$  (1 W). The power on the outermost sensor is negligible. The maximum variation of temperature in  $_{42}$  this conditions is around 6.5 °C.

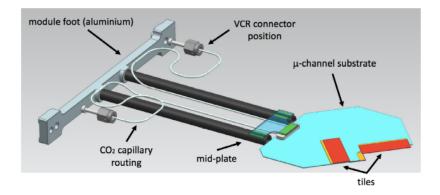

**Figure 2:** Realistic drawing of the micro-channels substrate with the mechanical support and tiles (sensor + ASICs). The whole substrate is held in place by the midplate glued on the back of the fluidic connector.

One of the most challenging stages of the research and development program was the attachment of the fluidic connector to the substrate. The connector is made of invar to minimize the thermal expansion mismatch and it is attached using a soldering technique. This attachment should be leak tight since the detector is under vacuum and the module is held by the back side of the connector, as illustrated in the Figure 2. Therefore, the planarity and parallelism between the connector and the substrate is important for the alignment. On top of that, flux can not be used since it could corrode the internal parts of the cooling system over the years of operation. The silicon

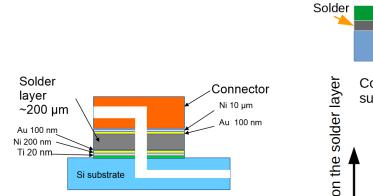

- $_{50}$  and connector are metalized with layers of titanium (20 nm, silicon only), nickel (0.2-10 $\mu$ m) and

- <sup>51</sup> gold (100 nm) to ensure a good attachment of the solder as illustrated in Figure 3. The soldering

- <sup>52</sup> parameters like pressure of the vacuum chamber and temperature cycle were optimized using more

- than 150 prototypes before finally achieving a reliable procedure that doesn't introduce significant

- $_{54}$   $\,$  stress in the solder joint. On the first soldered micro-channel substrate, a variation of only 11  $\mu m$

- <sup>55</sup> was found comparing the planarity measurement of the substrate before and after the soldering.

- <sup>56</sup> The measurement of the connector height with respect to the silicon surface showed that there is

- $_{57}$   $\,$  only a variation of 43  $\mu m,$  which can be easily absorbed by the glue layer to the support.

**Figure 3:** Cross section of the solder joint. The metallization is necessary to ensure a good attachment to both surfaces.

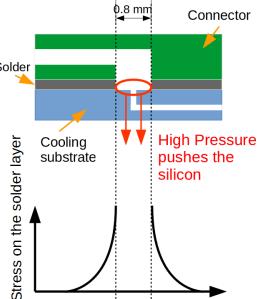

**Figure 4:** When the system contains high pressure coolant, the region indicated in red is pushed down and the stress is concentrated in the region around the input/ouput.

The solder joint was tested for two long term effects: creep and fatigue. Creep is the plastic deformation of the material under small mechanical stress levels. This effect is very dependent on temperature and mechanical load. It becomes relevant typically when the material is warmer than half of its melting temperature. Usually, it is a very slow effect that might take years or more. In the other hand, fatigue is the weakening of the material due to a repeatedly applied load. A good example of this effect are the cracks that appears in asphalt after temperature and pressure cycles.

The creep effect was accelerated using a higher mechanical load and temperature than in nominal conditions. Typically, the internal pressure applied was around 60 bar and the samples were kept at 120 °C. The high pressure is provided by a compressed air bottle and the sample is kept at high temperature using heaters. A model based on [4] can predict only the behavior of the creep effect at the linear stage. Based on this model, the acceleration factor using higher temperatures and loads was obtained. The failure of the material was arbitrary defined as 1% of elongation. Two cases were considered: even stress distribution over the whole solder joint (case A) or lo-

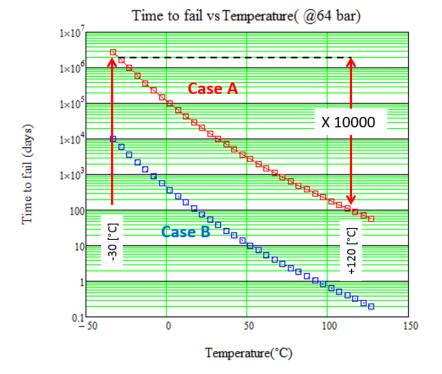

**Figure 5:** This plot represents the time necessary for the solder layer to elongate by 1% (failure) for a constant pressure of 64 bar as function of the temperature. The case A represents the result obtained when the mechanical stress is uniformly distributed over the whole solder surface and the case B is when the stress is localized on the region close to the input/ouput. One can notice that comparing the time of failure at -30 °C and +120 °C, this effect is accelerated by roughly a factor 10000.

calized stress around the input/output of the substrate (case B). The case B is more realistic as it 71 is illustrated in the Figure 4. The results are shown in the Figure 5. Both cases showed similar 72 acceleration factors of around  $\times 10000$  comparing with nominal conditions (-30 °C, 20 bar) and 73 accelerated conditions (120 °C, 60 bar). This means that 1 hour of accelerated test would corre-74 spond to more than 1 year in nominal conditions. In total, 18 samples were tested during 2630 75 hours ( $\sim 110$  days). Only two samples gave in during this test. The first one had a large void close 76 to one of the slits. Both samples were produced using an experimental technique with a significant 77 amout of flux. The first sample had a large void close to the slit. In the second sample, there was a 78 thin layer of flux between the solder and one of the surfaces. Therefore, the usage of flux can also 79 generate problems in the solder joint it self on the long term. The procedure used to solder the first 80 micro-channel doesn't use flux. 81

To simulate the fatique effect, a set-up composed of a chiller and 6 peltiers produces the temperature cycles from -40 °C and +60 °C. The high pressure provided by compressed air from a bottle was used to create pressure cycles from 1 up to 200 bar. In total, 5232 temperature cycles were performed on 9 samples. For every temperature cycle, 6 pressure cycles were performed. Only one sample didn't endure the cyclic test. This sample was soldered with an experimental technique using a significant amount of flux and very fast cooldown rate that could create internal stress. This sample resisted a single temperature cycle with maximum pressure upt to 60 bar and <sup>89</sup> gave in the second temperature cycle with pressure up to 100 bar.

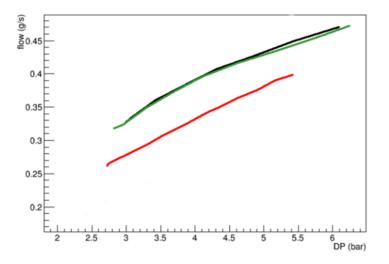

Since the cooling system is under vacuum, every couple of cooling loops can be isolated from 90 the other loops and the cooling plant by two pneumatic valves that will close if any leak is detected. 91 If too much liquid  $CO_2$  is trapped at cold temperature, this could lead to very high pressures as the 92 system absorbs heat mostly due to radiation. Therefore, a gas reservoir is necessary in between 93 the values in such way that the pressure just follows the saturation curve. This means that at room 94 temperature the pressure will be around 65 bar. The fluidic characteristics of the final system was 95 assessed using a dedicated set-up with realistic length of tubes for the input/output, safety valves, 96 expansion volume and the micro-channels. For the nominal flow of 0.4 g/s, a variation in pressure 97 of 4.2-5.3 bar was observed for the case where there is no power dissipation and the 30 W case, 98 respectively. The results are shown in Figure 7. 99

Figure 6: Experimental setup used to evaluate the cooling performance of the micro-channels.

**Figure 7:** Fluidic characterization of the micro-channels. This plot shows the  $CO_2$  flow through a single micro-channel as function of the pressure difference. The different colors represent the results obtained for 0 W (black), 5 W (green) and 30 W (red). For the nominal flow of 0.4 g/s, a difference in pressure between 4.2 and 5.3 bar is necessary.

#### 100 **3. Ceramic substrate**

One of the cooling substrate alternatices is a more conservative approach composed of a network of four parallel stainless steel capillaries with an outer diameter of 0.8 mm and wall thickness of 0.3 mm, which are brazed into a manifold. The entrance to the capillary network has 0.16 mm diameter orifices, which serve as an expansion point and ensures even distribution of the coolant. Then, the capillaries network is glued into a matching pattern of trenches manufactured inside a 1 mm thick aluminium nitride substrate to serve as mechanical and thermal interface to the electronics. The design is shown in the Figure 8.

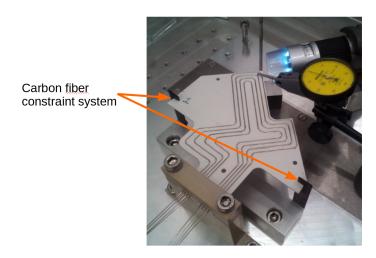

The thermal performance of a full-scale prototype has been recently tested with one quarter of the system glued with Stycast: 3 ASIC mockups + 1 sensor mockup (3 x 2W + 1W). A variation of 8 °C was found across the cooling substrate with respect to the temperature of the out going CO<sub>2</sub>. Since there are materials with different expansion coefficients (Shapal 4.8 × 10<sup>-6</sup>/K and stainless steel 16 × 10<sup>-6</sup>/K), a constraint system is necessary to prevent large deflections of the module due to temperature variations. The Figure 9 shows the constraint system on the sides of the cooling substrate. The deflections of the module were under 100 µm.

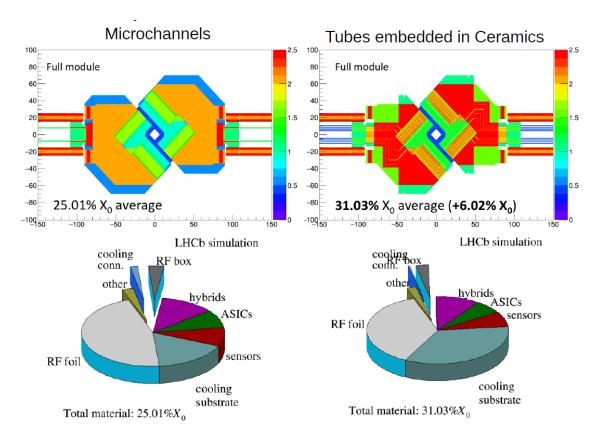

The material simulations have shown that the increase in the average material budget is only

around 6% of the radiation length ( $\chi_0$ ). For the VELO Upgrade a sizeable contribution comes from

the aluminum foil that separates the beam vacuum from the detector vacuum (RF foil). The results

<sup>118</sup> obtained are shown in the Figure 10.

**Figure 8:** Design of the ceramic substrate. The coolant flows through 4 stainless steel pipes of outer diameter of 0.8 mm and wall thickness of 0.3 mm.

Figure 9: Figure illustrating the constraint system in carbon fiber on the sides of the module.

**Figure 10:** Comparison of the material budget between the micro-channels embedded in silicon (left) and the ceramic substrate (right). A sizeable contribution comes from the RF foil that separates the beam vacuum from the detector vacuum.

# 119 4. 3D printing in Titanium

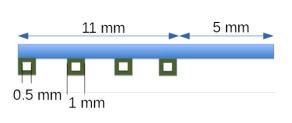

The advancements in the 3D printing allow creating structures that would be impossible a 120 few years ago. Today, a wide variaty of material can be used to print 3D objects. The second 121 substrate alternative is based in 3D printing using titanium. Its powder is fused using a laser beam 122 to form a 3D object layer by layer. The coolant circulates through four squared titanium tubes 123 that are just under the electronics like it is shown in the Figures 11 and 12. These substrates are 124 much faster to produce (quick prototyping). In a single batch that takes a few days, 25 modules 125 can be manufactured. They are also cheaper than the other cooling substrates previously described 126 in this document. The restrictions can be integrated in the inlet of the device (0.35 mm x 0.35 mm x)127 mm x 40 mm). It is also easier to handle than the silicon cooling substrate. However, it also 128 has disadvantages like low thermal conductivity (16 W/(m.K)) and mismatch of thermal expansion 129 coefficients with respect to the electronics  $(6 \times 10^{-6}/\text{K})$ . 130

**Figure 11:** Cross section of the design of the 3D printed substrate. The blue rectangle represents the sensor and ASIC glued on top of the four cooling Ti tubes.

**Figure 12:** Realistic drawing showing all the electronics components on top of the 3D printed Ti substrate.

High pressure tests showed that these structures can withstand up to 250 bar and leak tightness 131 can be obtained if the walls are at least  $250 \,\mu\text{m}$ . The deflections due to the temperature variations 132 are also below 100 µm. There are still many tests to be done to completely validate this alternative. 133 For instance, due to the limited area for the attachment of the electronics on the cooling substrate 134 the glue layer should be optimized in such way that it can provide a good attachment and at the same 135 time minimal variation of temperature. Flatness is also a concern since it is not a solid structure 136 and the manufacturing reproducibility still has to be proven. On top of that, it should be proven 137 that there is no detachment of the titanium powder over time. 138

### 139 5. Conclusion

The micro-channel evaporative cooling has a better physics performance due to the lower material budget. There is no CTE mismatch between the electronics and the substrate since the sensor and ASIC are also made of silicon. No fatigue or accumulated stresses were observed performing long term reliability tests. The first micro-channel substrate was properly attached to the fluidic connector recently.

Two back-up alternatives were designed to have similar fluidic characteristics and be easier to handle. The tubes embedded in ceramics is the most conservative approach and it has a good thermal performance but it would required a dedicated constraint system. On the other hand, the 3D Titanium printed substrate is evolving quite fast due to the fast prototyping and it is also cheaper than the other alternatives. All technologies are going to be reviewed on late September and the final decision will be taken shortly after.

### 151 References

152 [1] A. A. Alves Jr. et al. The LHCb detector at the LHC. JINST, 3:S08005, 2008.

- [2] LHCb Collaboration. LHCb VELO Upgrade Technical Design Report. Technical Report

CERN-LHCC-2013-021. LHCB-TDR-013, CERN, Nov 2013.

- 155 [3] ANSYS® Academic Research, Release 14.5, ANSYS, Inc.

- [4] X. Q. Shi, Z. P. Wang, W. Zhou, H. L. J. Pang, and Q. J. Yang. A new creep constitutive model for

eutectic solder alloy. *J. Electron. Packag 124(2), 85-90 (May 02, 2002), 2002.*