# Test results of irradiated CMOS pixel circuits in 150 nm CMOS technology for the ATLAS Inner Tracker Upgrade

# Zongde Chen<sup>1</sup>

Aix Marseille University, CNRS/IN2P3, CPPM, 163 Avenue de Luminy, Marseille, France E-mail: chenzd@cppm.in2p3.fr

M. Barbero<sup>a</sup>, P. Barrillon<sup>a</sup>, C. Bespin<sup>b</sup>, S. Bhat<sup>a</sup>, P. Breugnon<sup>a</sup>, I. Caicedo<sup>b</sup>, Y. Degerli<sup>c</sup>, S. Godiot<sup>a</sup>, T. Hemperek<sup>b</sup>, T. Hirono<sup>b</sup>, F.J. Iguaz<sup>c</sup>, H. Krüger<sup>b</sup>, P. Pangaud<sup>a</sup>, A. Rozanov<sup>a</sup>, P. Rymaszewski<sup>b</sup>, P. Schwemling<sup>c</sup>, M. Vandenbroucke<sup>c</sup>, T. Wang<sup>b</sup>, N. Wermes<sup>b</sup>

<sup>a</sup> Aix Marseille Univ, CNRS/IN2P3, CPPM, 163 Avenue de Luminy, Marseille, France <sup>b</sup> University of Bonn, Nussallee 12, Bonn, Germany <sup>c</sup> IRFU, CEA-Saclay, Gif-sur-Yvette Cedex, 91191 France

A major upgrade for the ATLAS Inner Tracker at the Large Hadron Collider (LHC) is scheduled in 2026. Depleted CMOS pixel sensors on high resistivity substrates in LFoundry 150 nm technology are an interesting option for this upgrade. Recently two large demonstrators, one based on a hybrid concept called LF-CPIX and the other based on a fully monolithic concept called LF-Monopix have been produced. Both prototypes were characterized in the lab and after irradiation up to 160 MRad under CERN's 24 GeV Proton Synchrotron beam. In this work, we will describe the behavior under radiation of the two prototypes.

*Topical Workshop on Electronics for Particle Physics (TWEPP2018)* 17-21 September 2018 Antwerp, Belgium

## <sup>1</sup>Speaker

© Copyright owned by the author(s) under the terms of the Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License (CC BY-NC-ND 4.0).

### 1. Introduction

The Inner Tracker (ITk) system of the ATLAS experiment will be upgraded for the 2026 High Luminosity Large Hadron Collider (HL-LHC) run. The HL-LHC will operate with a center of mass energy of 14 TeV and a peak instantaneous luminosity of  $7.5 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, five times higher than at present. The increased luminosity will result in roughly ten times higher radiation levels and data rates. To cope with the ATLAS requirements in terms of radiation hardness, readout speed and granularity at the HL-LHC, the replacement of the present ATLAS Inner Tracker (ITk) is needed. The ATLAS ITk Pixel Detector will consist in a silicon-based 5-layer cylinder with endcaps. While the 4 first layers (L0 to L3) will consist of hybrid-pixel detectors, an alternative option exists for the fifth layer (L4): a fully monolithic depleted-CMOS Pixel Detector concept. In this case, the sensor and the full readout logic circuitry are integrated into a single chip. On top of a potential for material reduction, one important advantage of this approach relates to the use of a monolithic concept translates in simpler production steps (e.g. no bumpbonding) and savings in production time, which might be a decisive factor given the schedule constraints of the project.

Two approaches are pursued within the ATLAS depleted CMOS sensor community. The first one is based on small collection electrodes and the second one on large collection electrodes concept. In the small collection electrode concept, the charge-collecting node is placed outside the CMOS circuitry, which reduces the input capacitance to the circuitry, and offers lower power budget for the analog front-end circuit. However, as charges need to travel longer distances to the collection node, the radiation-hardness of such a concept needs to be carefully assessed. In contrast, the large collection electrode design provides a Deep-Nwell (DNW), which embeds the electronics, and acts as a charge-collecting node. This results in a more uniform electric field in the bulk and shorter drift distance and leads to better radiation hardness. The price to pay is a larger input capacitance to the electronics and the need for careful study of sensor to electronics coupling.

This work presents two large collection electrode concept prototypes, named LF-CPIX and LF-Monopix which were developed in LFoundry 150 nm CMOS technology on a high resistivity (> $2K\Omega \cdot cm$ ) wafer. The second section will give a brief overview of both prototypes. In section 3, measurement results for both prototypes in laboratory and under the proton radiation of 160 MRad will be shown. A summary is given in section 4.

## 2. Prototypes developed in LF technology

### 2.1 LF-CPIX

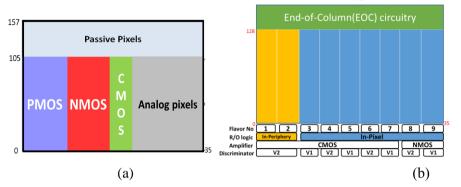

The LF-CPIX demonstrator was developed based on the promising results of a previous prototype called CCPD\_LF [1]. In the LF-CPIX prototype, the guard-ring strategy was optimized in order to increase the reverse breakdown voltage of the chip as well as reduce the inactive region; it is based on TCAD simulation [2]. The LF-CPIX chip implements these new ideas on the sensor structure, as well as several flavors of analog front-ends. The chip and pixel sizes are 10 mm×10 mm and 250  $\mu$ m×50  $\mu$ m, respectively [3].

Each pixel of LF-CPIX is composed of a charge sensitive amplifier (CSA) as the amplifying stage, a source follower and a discriminator. In order to correct for the threshold dispersion, a 4-

bit threshold tuning DAC (TDAC) sits in each pixel, and enables locally the tuning of the threshold value of each pixel. A register (HIT register) is also implemented in each pixel, which can store the discriminator hit information, so that threshold scan test can be performed without full complex readout logic circuitry. The pixel matrix has three different pixel types, with different input transistors for each sub-array (NMOS, PMOS and CMOS inputs).

Figure 1: a) Sketch of the LF-CPIX with different sub-array flavors. b) Sketch of the LF-Monopix with different sub-array flavors.

### 2.2 LF-Monopix

The LF-Monopix chip was the first fully monolithic prototype implemented in LFoundry 150 nm CMOS technology [4]. It inherits the analog and sensor parts of LF-CPIX chip, and integrates them with a fast readout logic, similar to the FE-I3 readout architecture. The chip and pixel size are 10 mm×10 mm and 250  $\mu$ m×50  $\mu$ m, respectively. The pixel matrix consists in nine different flavors, which differ by the designs of their CSA (2 types: NMOS transistor input and CMOS complementary input), the discriminator architecture (2 types: two stage open-loop structure and a self-biased differential amplifier with a CMOS output stage) and the placement of the pixel readout circuitry (2 types: in-pixel and in periphery).

### 3. Prototype characterization

### **3.1 LF-CPIX measurement results**

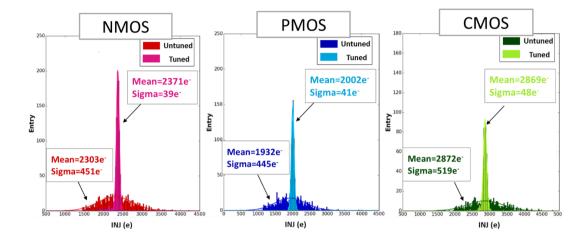

LF-CPIX was tested in the laboratory at room temperature. The breakdown voltage is around -230V at room temperature, which is an improved value with respect to previous prototype in this technology and matches simulation results [2]. A fully depleted thin sensor, e.g. 100  $\mu$ m, biased via backside can be achieved [4]. Threshold scans and TDAC tunings were performed, for all flavors, which worked well and the threshold spread for all three flavors reduced from over 300 e<sup>-</sup> to 60 e<sup>-</sup> after tuning. The electronics noise is roughly 120 e<sup>-</sup> for the whole matrix.

In order to investigate the radiation hardness of the prototype, LF-CPIX samples were irradiated at the 24 GeV Proton Synchrotron beam in CERN at room temperature up to a total ionizing dose (TID) of 150 MRad and Non-Ionizing Energy Loss (NIEL) of  $3.45 \times 10^{15} n_{eq} \cdot cm^{-2}$ . This value is roughly 2 times the dose expected for the L4 lifetime before replacement in ITk. During irradiation, the CSA and discriminator outputs were monitored; the samples were fully functional for the whole radiation period.

### Zongde Chen

Threshold scans were performed after irradiation for all the flavors (see Figure 2). After irradiating the samples up to 150 MRad, threshold mean value for all the flavors is between 2 ke<sup>-</sup> to 3 ke<sup>-</sup> with a dispersion of less than 50e<sup>-</sup>.

Figure 2: Threshold distribution before and after tuning with TID of 150 MRad

### 3.2 LF-Monopix measurement results

Similar measurements were performed on LF-Monopix samples. The chip is fully functional, the sensor part, analog part and the readout circuits work correctly. The breakdown voltage of LF-Monopix at room temperature was around -280V. Threshold scans were performed for the whole matrix in the laboratory, threshold dispersion differs by flavors. However, all the flavors of pixels with fully integrated read-out logic can be tuned with a dispersion less than 100 e<sup>-</sup>. The noise value for different flavors falls between 180 e<sup>-</sup> and 280 e<sup>-</sup>.

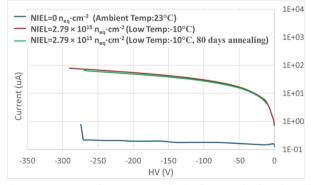

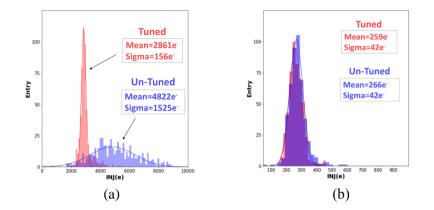

To understand the NIEL and TID effects, LF-Monopix samples were irradiated at the 24 GeV Proton Synchrotron beam in CERN up to a TID of 160 MRad and NIEL of  $2.79 \times 10^{15}$  n<sub>eq</sub>·cm<sup>-2</sup>. As expected, we observed an increase of the leakage current as shown in Figure 3. For example, at -100 V, the current went from 18 nA before irradiation to 25  $\mu$ A (5.3 nA/pixel) after NIEL of  $2.79 \times 10^{15}$  n<sub>eq</sub>·cm<sup>-2</sup>. Threshold scans and TDAC tunings were done for the whole matrix. Figure 4 shows an example of the results obtained for the flavor 8 (NMOS input transistor + self-biased differential amplifier with a CMOS output stage discriminator): The threshold dispersion reduced from 1525 e<sup>-</sup> to 156 e<sup>-</sup> after tuning, threshold mean value was tuned from 4822e<sup>-</sup> to 2861 e<sup>-</sup>; the electronics noise stayed at roughly 260 e<sup>-</sup> before and after tuning.

Figure 3: I-V curve of LF-Monopix before and after irradiation.

Figure 4: Threshold scan and tuning after 160 MRad proton irradiation. Threshold distribution (a) and Noise distribution (b) before and after tuning

### 4. Summary

Two prototype chips namely LF-CPIX and LF-Monopix have been produced in the LFoundry 150 nm process. Before irradiation, both chips were fully functional, with breakdown voltages measured below -230 V. The two prototypes have been irradiated TID over 150 MRad and NIEL over  $2.7 \times 10^{15}$  n<sub>eq</sub>·cm<sup>-2</sup> at the 24 GeV Proton Synchrotron beam in CERN. The chips have shown good radiation tolerance although measurements and tunings for all irradiated LF-Monopix flavors are still ongoing. Based on these positive results, a next demonstrator submission is being planned which will study the possibility to reduce the pixel size, improve the analog pixel frontend, assess various readout architecture possibilities, and develop several peripheral blocks needed towards a final IC for use in the ATLAS ITk Pixel detector L4.

### Acknowledgments

This work has received funding from the European Union's Horizon 2020 Research and Innovation programme under Grant Agreements no.675587-STREAM. Many thanks for support received from the AIDA-2020 Advanced European Infrastructures for Detectors at Accelerators project from the European Union's Horizon 2020 Research and Innovation programme under Grant Agreement no. 654168.

## References

- Hirono T et al, Characterization of fully depleted CMOS active pixel sensors on high resistivity substrates for use in a high radiation environment, Nuclear Science Symposium, Medical Imaging Conference and Room-Temperature Semiconductor Detector Workshop (NSS/MIC/RTSD), 2016. IEEE, 2016: 1-4.

- [2] J. Liu et al., Simulations of depleted CMOS sensors for high-radiation environments, JINST 12 (2017) C11013.

- [3] Y. Degerli et al., Pixel architectures in a HV-CMOS process for the ATLAS inner detector upgrade, JINST 11 (2016) C12064.

- [4] T. Wang et al., Development of a Depleted Monolithic CMOS Sensor in a 150 nm CMOS Technology for the ATLAS Inner Tracker Upgrade, JINST 12 (2017) C01039, [1611.01206].